#### Rev C1, Page 1/66

#### FEATURES

- Integrated Hall sensors for two-track scanning

- Hall sensors optimized for 1.50 mm pole width (master track)

- Signal conditioning for offset, amplitude, and phase

- Sine/digital real-time conversion with 12-bit resolution (14-bit filtered)

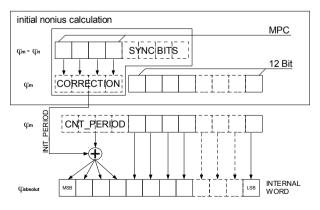

- ♦ 2-track nonius absolute value calculation up to 18 bits

- ♦ 16, 32, or 64 pole pairs per measurement distance

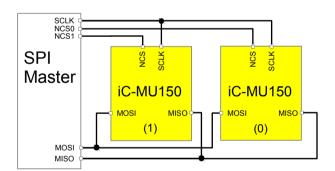

- Enlargement of measurement distance with second iC-MU150

- Synchronization of external multiturn systems

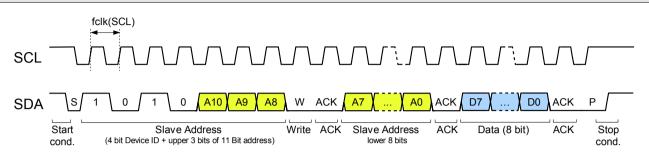

- Configuration from an external EEPROM using a multimaster I2C interface

- Microcontroller-compatible serial interface (SPI, BiSS, SSI)

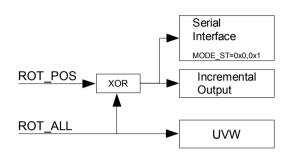

- Incremental quadrature signals with an index (ABZ)

- ♦ FlexCount<sup>®</sup>: scalable resolution from 1 up to 65536 CPR

- Commutation signals for motors from 1 up to 16 pole pairs (UVW)

#### APPLICATIONS

- Rotative absolute encoders

- Linear absolute scales

- Singleturn and multiturn encoders

- Motor feedback encoders

- BLDC motor commutation

- Hollow shaft encoder

- Multi-axis measurement systems

#### PACKAGES

5 mm x 5 mm x 0.9 mm 7 mm x 7 mm x 0.9 mm RoHS compliant RoHS compliant

#### DESCRIPTION

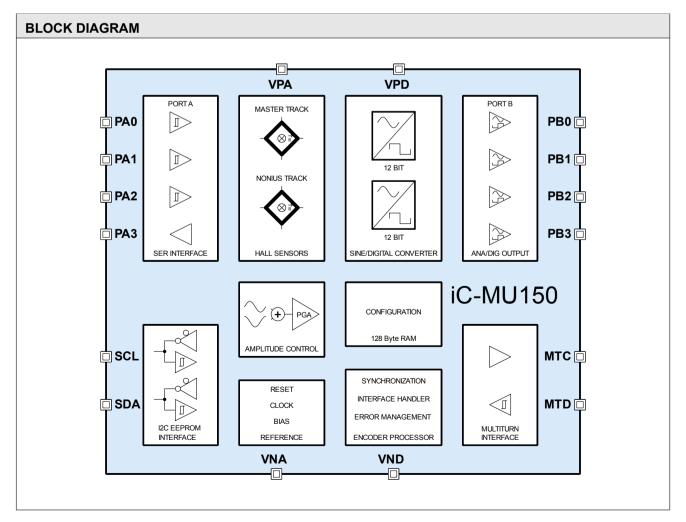

iC-MU150 is used for magnetic off-axis position definition with integrated Hall sensors. By scanning two separate channels i.e. the master and nonius track the device can log an absolute position within one mechanical revolution. The chip conditions the sensor signals and compensates for typical signal errors.

The internal 12-bit sine/digital converters generate two position words that supply high-precision position data within one sine-period. The integrated nonius calculation engine calculates the absolute position within one mechanical revolution and synchronizes this with the master track position word. Position data can be transmitted serially, incrementally, or analog through two ports in various modes of operation. Commutation signals for brushless DC (BLDC) motors with up to 16 pole pairs are derived from the absolute position and supplied through a 3-pin interface.

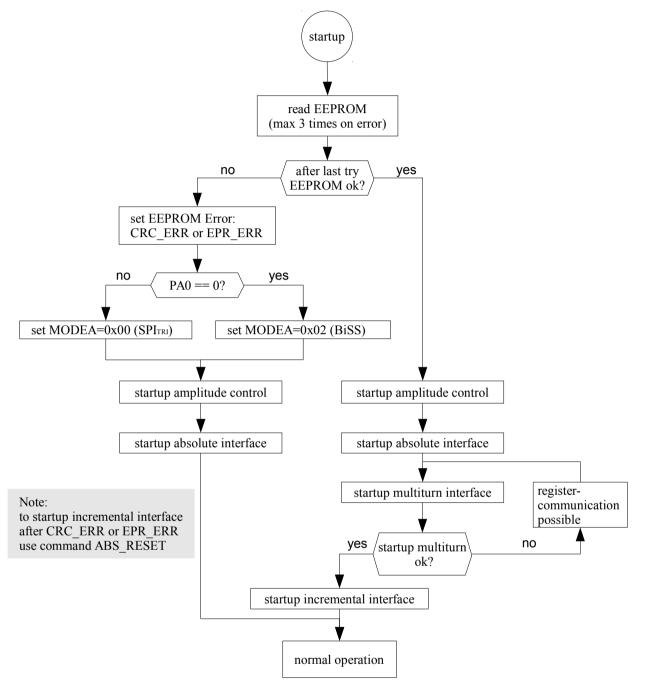

During startup the device loads a CRC-protected configuration from an external EEPROM.

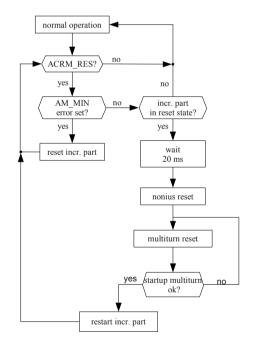

After the device has been reset an optional external multiturn is read in an synchronized with the internal position data. During operation the position is cyclically checked.

The device offered here is a multifunctional iC that contains integrated BiSS C interface components. The BiSS C process is protected by patent DE 10310622 B4 owned by iC-Haus GmbH. Users benefit from the open BiSS C protocol with a free license which is necessary when using the BiSS C protocol in conjunction with this iC.

Download the license at www.biss-interface.com/bua

| PACKAGING INFORMATION<br>PIN CONFIGURATION DFN16-5x5           | 5  |

|----------------------------------------------------------------|----|

| (topview)                                                      | 5  |

| PIN CONFIGURATION QFN48-7x7<br>(topview)                       | 5  |

| PACKAGE DIMENSIONS DFN16-5x5                                   | 6  |

| PACKAGE DIMENSIONS QFN48-7x7                                   | 7  |

| ABSOLUTE MAXIMUM RATINGS                                       | 8  |

| THERMAL DATA                                                   | 8  |

| ELECTRICAL CHARACTERISTICS                                     | 9  |

| OPERATING REQUIREMENTS                                         | 11 |

| Multiturn Interface                                            | 11 |

| I/O Interface                                                  | 12 |

| PRINCIPLE OF MEASUREMENT                                       | 14 |

| Rotative measuring system                                      | 14 |

| Linear measuring system                                        | 14 |

| CONFIGURATION PARAMETERS                                       | 15 |

| REGISTER ASSIGNMENTS (EEPROM)                                  | 17 |

| Register assignment (EEPROM)                                   | 17 |

| Special BiSS registers                                         | 19 |

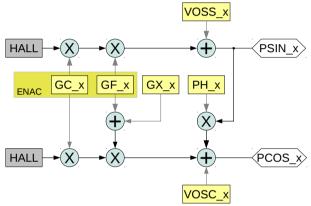

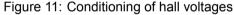

| SIGNAL CONDITIONING FOR MASTER AND<br>NONIUS CHANNELS: x = M,N | 20 |

| Bias current source                                            | 20 |

| Gain settings                                                  | 20 |

| Offset compensation                                            | 21 |

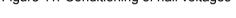

| Phase adjustment                                               | 21 |

| ANALOG SIGNAL CONDITIONING FLOW: x =<br>M,N                    | 22 |

| 1. Conditioning the BIAS current                               | 22 |

| 2. Positioning of the sensor                                   | 22 |

| 3.a Test modes analog master and analog nonius                 | 22 |

| 3.b Test mode CNV_x                                            | 22 |

| 4. Track offset SPON                                           | 23 |

| EEPROM AND I2C INTERFACE                                       | 24 |

| Basic interface features                                       | 24 |

| EEPROM device requirements                                     | 24 |

| CRC checksums                                                  | 24 |

| <b>C</b> Haus |

|---------------|

|---------------|

Rev C1, Page 3/66

| STARTUP BEHAVIOR                                               | 26  |

|----------------------------------------------------------------|-----|

| CONFIGURABLE I/O INTERFACE                                     | 28  |

| Setting the interfaces                                         | 28  |

| Serial interface:                                              |     |

| Configuring the data format and data                           |     |

| length                                                         | 29  |

| BiSS C interface                                               | 31  |

| SSI interface                                                  | 32  |

| SPI interface: general description                             | 34  |

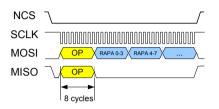

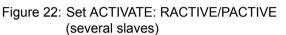

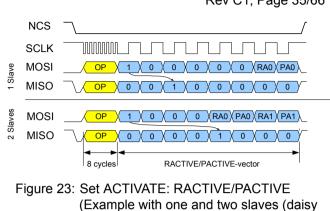

| SPI interface: Command ACTIVATE                                | 34  |

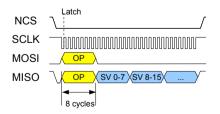

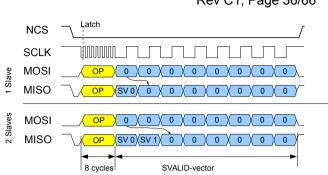

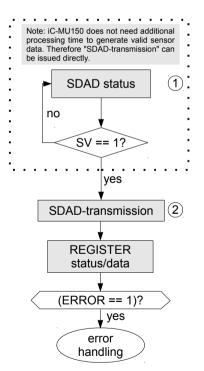

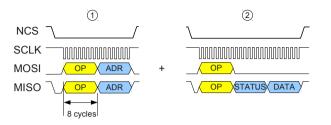

| SPI interface: Command SDAD transmission                       | 35  |

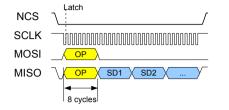

| SPI interface: Command SDAD status                             | 36  |

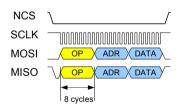

| SPI interface: Command Read REGISTER                           | ~ ~ |

|                                                                | 36  |

| SPI interface: Command Write REGISTER (single)                 | 37  |

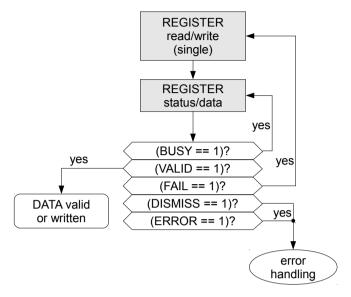

| SPI interface: Command REGISTER                                | 51  |

| status/data                                                    | 37  |

| CONVERTER AND NONIUS CALCULATION                               | 39  |

| Converter principle                                            | 39  |

| Synchronization mode                                           | 39  |

|                                                                | 42  |

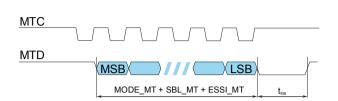

| Configuration of the Multiturn interface                       | 42  |

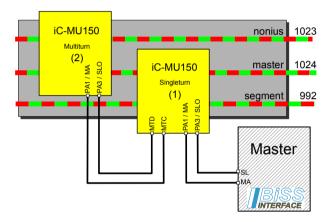

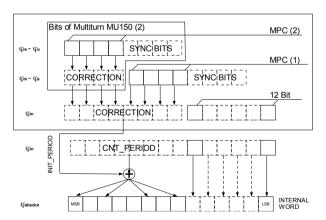

| Construction of a Multiturn system with two                    | 74  |

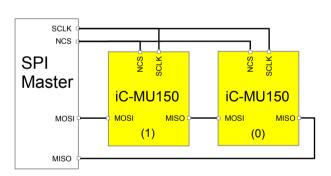

| iC-MU150                                                       | 43  |

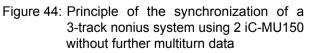

| MT Interface Daisy Chain                                       | 45  |

| INCREMENTAL OUTPUT ABZ,                                        |     |

| STEP/DIRECTION AND CW/CCW                                      | 46  |

| UVW COMMUTATION SIGNALS                                        | 49  |

|                                                                |     |

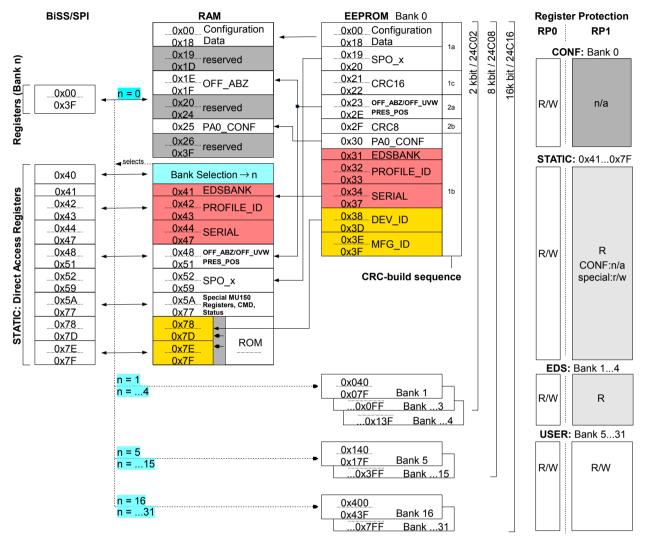

| REGISTER ACCESS THROUGH SERIAL<br>INTERFACE (SPI AND BISS)     | 50  |

| Register mapping Configuration, Bank 0:<br>Addresses 0x00-0x3F | 50  |

| Register mapping static part: Addresses<br>0x40-0xBF           | 52  |

| Address sections/Register protection level                     | 54  |

| Overview Register access: memory mapping,                      | 51  |

| Register protection levels                                     | 55  |

| STATUS REGISTER AND ERROR MONITORING                           | 56  |

| Status register                                                | 56  |

| Error and warning bit configuration                            | 56  |

Rev C1, Page 4/66

| COMMAND REGISTER                              | 58 | F   |

|-----------------------------------------------|----|-----|

| Description of implemented commands           | 58 |     |

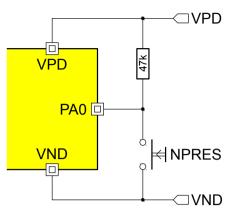

| Configurable NPRES Pin                        | 61 | DES |

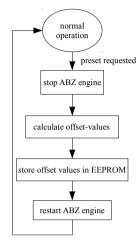

| POSITION OFFSET VALUES AND PRESET<br>FUNCTION | 62 | REV |

| Preset function                        | 62 |

|----------------------------------------|----|

| DESIGN REVIEW: Notes On Chip Functions | 64 |

| REVISION HISTORY                       | 65 |

Rev C1, Page 5/66

#### PACKAGING INFORMATION

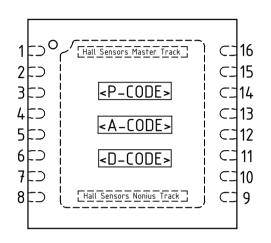

# PIN CONFIGURATION DFN16-5x5 (topview)

#### PIN FUNCTIONS No. Name Function

- 1 SCL EEPROM interface, clock

- 2 SDA EEPROM interface, data

- 3 VPA +4.5 V...+5.5 V analog supply voltage

- 4 VNA<sup>1)</sup> Analog Ground

- 5 PB0 Port B, Pin 0: Digital I/O, analog output

- 6 PB1 Port B, Pin 1: Digital I/O, analog output

- 7 PB2 Port B, Pin 2: Digital I/O, analog output

- 8 PB3 Port B, Pin 3: Digital I/O, analog output

- 9 PA3 Port A, Pin 3: Digital I/O

- 10 PA2 Port A, Pin 2: Digital I/O

- 11 PA1 Port A, Pin 1: Digital I/O 12 PA0 Port A, Pin 0: Digital I/O

- 12 PAU POILA, PIILU. Digita

- 13 VND<sup>1)</sup> Digital ground

- 14 VPD +4.5 V...+5.5 V digital supply voltage

- 15 MTD Multiturn interface, data input

- 16 MTC Multiturn interface, clock output BP<sup>2)</sup> Backside Pad

IC top marking: <P-CODE> = product code, <A-CODE> = assembly code (subject to changes), <D-CODE> = date code (subject to changes); 1) Analog (VNA) and digital grounds (VND) have to be connected low ohmic on the PCB.

- 2) The backside pad on the underside of the package should be appropriately connected to VNA/VND for better heat dissipation (ground plane).

- 3) Only the Pin 1 mark on the front or reverse is determinative for package orientation (<P-CODE>, <A-CODE>, <D-CODE> are subject to change).

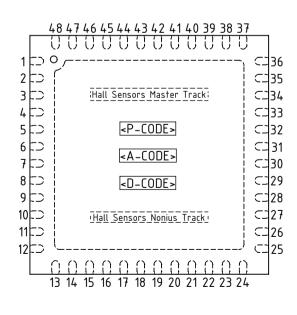

# PIN CONFIGURATION QFN48-7x7 (topview)

## PIN FUNCTIONS

| 3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11-26<br>27<br>28<br>29<br>30<br>31<br>32<br>33 | PA3<br>PA2<br>PA1<br>PA0<br>VND <sup>1)</sup><br>VPD<br>MTD | not connected<br>EEPROM interface, clock<br>EEPROM interface, data<br>+4.5 V+5.5 V analog supply voltage<br>Analog Ground<br>Port B, Pin 0: Digital I/O, analog output<br>Port B, Pin 1: Digital I/O, analog output<br>Port B, Pin 2: Digital I/O, analog output<br>Port B, Pin 3: Digital I/O, analog output<br>not connected<br>Port A, Pin 3: Digital I/O<br>Port A, Pin 2: Digital I/O<br>Port A, Pin 1: Digital I/O<br>Port A, Pin 1: Digital I/O<br>Port A, Pin 0: Digital I/O<br>Digital ground<br>+4.5 V+5.5 V digital supply voltage<br>Multiturn interface, data input |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34<br>35-48                                                                              | MTC<br>n.c.<br>BP <sup>2)</sup>                             | Multiturn interface, clock output<br>not connected<br>Backside Pad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                          |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

IC top marking: <P-CODE> = product code, <A-CODE> = assembly code (subject to changes), <D-CODE> = date code (subject to changes);

1) Analog (VNA) and digital grounds (VND) have to be connected low ohmic on the PCB.

2) The backside pad on the underside of the package should be appropriately connected to VNA/VND for better heat dissipation (ground plane).

3) Only the Pin 1 mark on the front or reverse is determinative for package orientation (<P-CODE>, <A-CODE>, <D-CODE> are subject to change).

Rev C1, Page 6/66

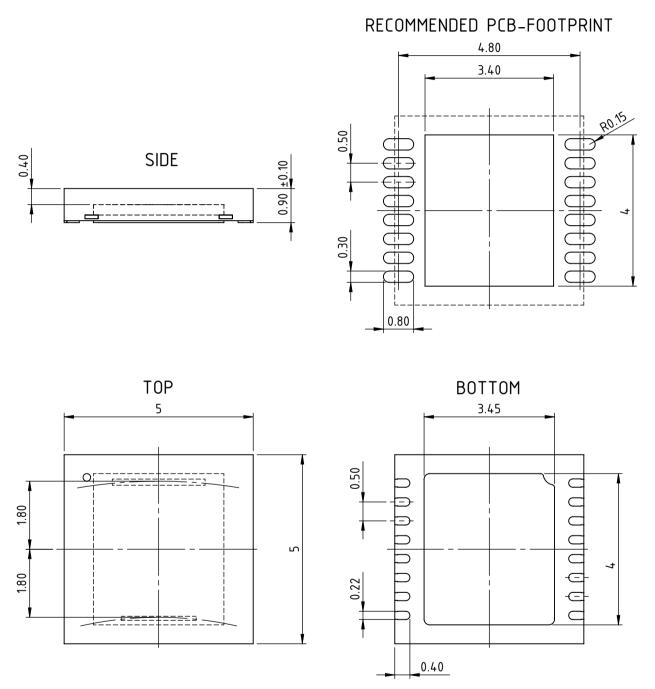

#### PACKAGE DIMENSIONS DFN16-5x5

All dimensions given in mm. Tolerances of form and position according to JEDEC M0–229. Positional tolerance of sensor pattern: ±0.10mm / ±1° (with respect to center of backside pad).

drb\_dfn16-5x5-2\_mu\_1\_pack\_1, 10:1

Rev C1, Page 7/66

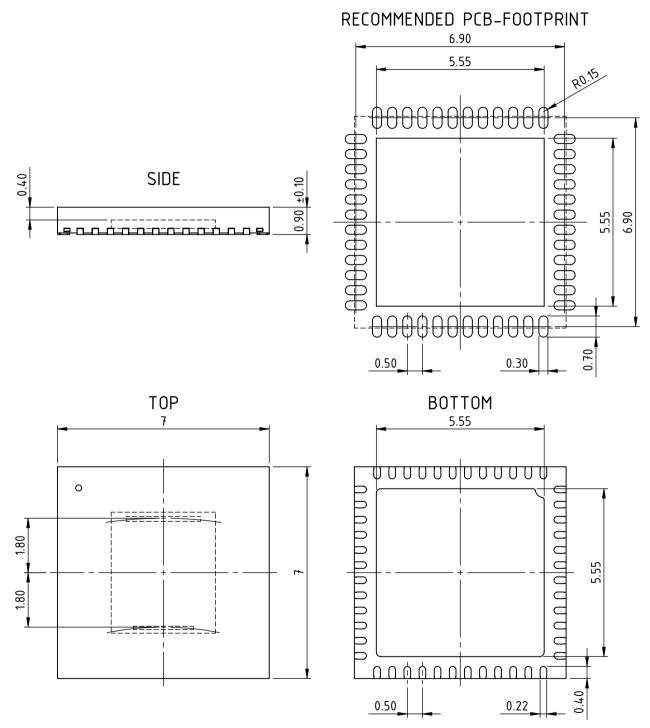

#### PACKAGE DIMENSIONS QFN48-7x7

All dimensions given in mm. Tolerances of form and position according to JEDEC MO-220. Positional tolerance of sensor pattern: ±0.10mm / ±1° (with respect to center of backside pad). drb\_qfn48-7x7-2\_mu\_y2\_pack\_1, 8:1

Rev C1, Page 8/66

#### **ABSOLUTE MAXIMUM RATINGS**

Maximum ratings do not constitute permissible operating conditions; functionality is not guaranteed. Exceeding the maximum ratings can damage the device

| Item | Symbol | Parameter                      | Conditions                                    |             |           | Unit     |

|------|--------|--------------------------------|-----------------------------------------------|-------------|-----------|----------|

| No.  |        |                                |                                               | Min.        | Max.      |          |

| G001 | V()    | Voltage at VPA, VPD            |                                               | -0.3        | 6         | V        |

| G002 | I()    | Current in VPA                 |                                               | -10         | 20        | mA       |

| G003 | I()    | Current in VPD                 |                                               | -10         | 100       | mA       |

| G004 | V()    | Voltage at all pins except VPD |                                               | -0.3        | VPD+0.3   | V        |

| G005 | I()    | Current in all I/O pins        | DC current<br>Pulse width < 10 µs             | -10<br>-100 | 10<br>100 | mA<br>mA |

| G006 | Vd()   | ESD Susceptibility at all pins | HBM, 100 pF discharged through $1.5  k\Omega$ |             | 2         | kV       |

| G007 | Ptot   | Permissible Power Dissipation  |                                               |             | 400       | mW       |

| G008 | Tj     | Chip-Temperature               |                                               | -40         | 150       | °C       |

| G009 | Ts     | Storage Temperature Range      |                                               | -40         | 150       | °C       |

#### THERMAL DATA

#### Operating conditions: VPA = VPD = $5 V \pm 10\%$

| Item | Symbol Parameter Conditions | Parameter                                   |                                                                                           |            |      | ditions    |          |  | Unit |

|------|-----------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------|------------|------|------------|----------|--|------|

| No.  |                             |                                             |                                                                                           | Min.       | Тур. | Max.       |          |  |      |

| T01  | Та                          | Operating Ambient Temperature Range         | DFN16-5x5<br>QFN48-7x7                                                                    | -40<br>-40 |      | 110<br>115 | 2°<br>2° |  |      |

| T02  | Rthja                       | Thermal Resistance Chip to Ambient<br>DFN16 | Surface mounted, Thermal-Pad soldered to approx. 2 cm <sup>2</sup> copper area on the PCB |            | 40   |            | K/W      |  |      |

| T03  | Rthja                       | Thermal Resistance Chip to Ambient QFN48    | QFN48-7x7 soldered to PCB according to<br>JEDEC 51                                        |            | 30   |            | K/W      |  |      |

Rev C1, Page 9/66

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VPD = VPA = 5 V  $\pm$ 10%, Tj = -40...125°C, IBP calibrated to 200  $\mu$ A, reference is VNA = VND, unless otherwise stated

| ltem<br>No. | Symbol         | Parameter                                             | Conditions                                                                                                                     | Min.         | Тур.                       | Max.                   | Unit              |

|-------------|----------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------|------------------------|-------------------|

| Total I     | Device         | I                                                     | 1                                                                                                                              | 0            |                            | 1                      |                   |

| 101         | V(VPA,<br>VPD) | Permissible Supply Voltage                            | VPA = VPD                                                                                                                      | 4.5          | 5                          | 5.5                    | V                 |

| 103         | I(VPA)         | Analog Supply Current in VPA                          |                                                                                                                                | 8            | 13                         | 16                     | mA                |

| 104         | I(VPD)         | Digital Supply Current in VPD                         |                                                                                                                                | 20           | 40                         | 65                     | mA                |

| 105         | Vc()hi         | Clamp Voltage hi at all pins                          | Vc()hi = V() - V(VPD), I() = +1 mA                                                                                             | 0.3          |                            | 1.6                    | V                 |

| 106         | Vc()lo         | Clamp Voltage lo at all pins                          | l() = -1 mA                                                                                                                    | -1.6         |                            | -0.3                   | V                 |

| 107         | ton()          | Power-Up Time                                         | VPD > 4 V, EEPROM Data valid after first $I^2C$ read in                                                                        |              | 20                         |                        | ms                |

| 108         | ΔV/Δt          | Power-Up Slew Rate at VPA =<br>VPD                    | V() = 3.0 V $ ightarrow$ 4.5 V                                                                                                 | 50           |                            |                        | V/s               |

| 109         | CVPA,<br>CVPD  | Required Backup Capacitors at VPA, VPD                | placed near by pin, recommended low ESR                                                                                        |              | 100                        |                        | nF                |

| Hall S      | ensors         |                                                       |                                                                                                                                |              |                            |                        |                   |

| 201         | Hext           | Operating Magnetic Field<br>Strength                  | at surface of chip                                                                                                             | 15           |                            | 100                    | kA/m              |

| 202         | f()            | Operating Magnetic Field Fre-<br>quency               |                                                                                                                                |              |                            | 7                      | kHz               |

| 203         | rpm            | Permissible rotation of pole<br>wheel with FRQ_CNV=lo | 16 pole pairs<br>32 pole pairs<br>64 pole pairs<br>(note: for incremental part see table 84)                                   |              |                            | 24000<br>12000<br>6000 | rpm<br>rpm<br>rpm |

| 204         | vmax           | Permissible movement speed                            |                                                                                                                                |              |                            | 20                     | m/s               |

| 205         | hpac           | Sensor-to-Package-Surface<br>Distance                 |                                                                                                                                |              | 400                        |                        | μm                |

| Assen       | nbly Tolera    | nces                                                  | ^                                                                                                                              |              |                            |                        |                   |

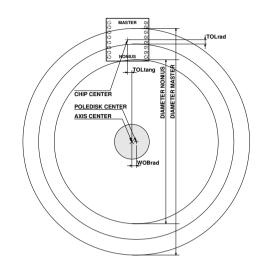

| 301         | TOLrad         | Permissible Radial Displacement                       |                                                                                                                                |              |                            | 0.5                    | mm                |

| 302         | TOLtan         | Permissible Tangential Displace-<br>ment              |                                                                                                                                |              |                            | 0.5                    | mm                |

| 303         | WOBrad         | Permissible Excentricity of Code<br>Disc              | MPC = 0x4<br>MPC = 0x5, 0x6                                                                                                    |              |                            | 0.06<br>0.1            | mm<br>mm          |

| Bias C      | urrent Sou     | rce, Reference Voltage, Power O                       | n Reset, Clock Oscillator                                                                                                      |              |                            |                        |                   |

| 401         | Vbg            | Bandgap Voltage                                       | TEST = 0x1F                                                                                                                    | 1.18         | 1.24                       | 1.36                   | V                 |

| 402         | Vref           | Reference Voltage                                     | TEST = 0x1F                                                                                                                    | 45           | 50                         | 55                     | %VPA              |

| 403         | IBM            | Reference Current                                     | CIBM = 0x0<br>CIBM = 0xF<br>IBM calibrated                                                                                     | -370<br>-220 | -200                       | -100<br>-180           | μΑ<br>μΑ<br>μΑ    |

| 404         | VPDon          | Turn-on Threshold VPD<br>(power on release)           | increasing voltage at V(VPD)                                                                                                   | 3.65         | 3.9                        | 4.3                    | V                 |

| 405         | VPDoff         | Turn-off Threshold VPD (power down reset)             | decreasing voltage at V(VPD)                                                                                                   | 3            | 3.5                        | 3.8                    | V                 |

| 406         | VPDhys         | Hysteresis                                            | VPDhys = VPDon - VPDoff                                                                                                        | 0.3          |                            |                        | V                 |

| 407         | fosc           | Clock Frequency                                       | TEST=0x26, fosc = 64*f(HCLK), IBM aligned                                                                                      | 22           | 26                         | 32                     | MHz               |

| 408         | tchk           | Max. Time For Internal Cyclic<br>Checks               | NCHK_NON = 0x0, CHK_MT = 0x1,<br>NCHK_CRC = 0x0, MODE_MT = 0xF (18 bit),<br>SBL_MT = 0x3 (4 bit), ESSI_MT = 0x1 (Error<br>bit) |              |                            | 6                      | ms                |

| Signa       | Conditioni     | ng Master and Nonius Track (x =                       | M, N)                                                                                                                          |              |                            |                        |                   |

| 501         | GC             | Adjustable Gain Range                                 | GC_x = 0x0<br>GC_x = 0x1<br>GC_x = 0x2<br>GC_x = 0x3                                                                           |              | 4.4<br>7.7<br>12.4<br>20.6 |                        |                   |

| 502         | GF             | Adjustable Fine Gain Range                            | GF_x = 0x00<br>GF_x = 0x20<br>GF_x = 0x3F                                                                                      |              | 1<br>4.4<br>19             |                        |                   |

Rev C1, Page 10/66

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VPD = VPA = 5 V  $\pm$ 10%, Tj = -40...125°C, IBP calibrated to 200  $\mu$ A, reference is VNA = VND, unless otherwise stated

| tem<br>No. | Symbol        | Parameter                                  | Conditions                                                         | Min.  | Тур.      | Max.     | Unit   |

|------------|---------------|--------------------------------------------|--------------------------------------------------------------------|-------|-----------|----------|--------|

| 503        | GX            | Adjustable Gain(SIN)/Gain(COS)             | GX_x = 0x00                                                        |       | 0         |          | %      |

|            |               |                                            | GX_x = 0x3F<br>GX_x = 0x7F                                         | 9     | 10<br>-9  | -8.5     | %<br>% |

| 504        | VOS           | Adjustable Offset Calibration              | VOS_x= 0x3F                                                        | 60    | 70        | -0.5     | mV     |

| 504        | 1000          |                                            | VOS_x= 0x3F<br>VOS_x= 0x7F                                         | 00    | -70       | -60      | mV     |

| 505        | PHM           | Adjustable Phase Calibration               | PH_M = 0x3F                                                        | 8     | 10        |          | 0<br>0 |

|            |               | Master Track                               | PH_M = 0x7F<br>PH_M = 0xBF                                         | 15.5  | -10<br>18 | -8       | 0      |

|            |               |                                            | $PH_M = 0xFF$                                                      | 15.5  | -18       | -15.5    | •      |

| 506        | PHN           | Adjustable Phase Calibration               | PH_N = 0x3F                                                        | 11.25 | 13        |          | 0      |

|            |               | Nonius Track                               | PH_N = 0x7F                                                        | 0.0   | -13       | -11.25   | 0      |

|            |               |                                            | $PH_N = 0xBF$<br>$PH_N = 0xFF$                                     | 20.5  | 23<br>-23 | -20.5    | 0      |

| 507        | Vampl         | Signal Level Controller                    | chip internally, Vampl =                                           | 3.2   | 4         | 4.8      | Vp     |

|            | , and         |                                            | Vpp(PSINx)+Vpp(NSINx), ENAC = 1                                    | 0.2   |           |          |        |

| 508        | Vae()lo       | Signal Monitoring Threshold lo             | Vae()lo = Vpp(PSINx)+Vpp(NSINx)                                    | 1.2   |           | 2.8      | Vpp    |

| 509        | Vae()hi       | Signal Monitoring Threshold hi             | Vae()hi = Vpp(PSINx)+VPP(NSINx)                                    | 5     |           | 6.3      | Vpp    |

| Sine-1     | To-Digital Co | onversion                                  |                                                                    |       |           |          |        |

| 601        | Aabs          | Absolute Angular Accuracy                  | ideal input signals, reference to 12 Bit of sine period            |       |           | 2        | LSE    |

| 602        | Arel          | Relative Angular Accuracy                  | FILT = 0x2                                                         |       |           | 2        | LSE    |

|            |               |                                            | FILT = 0x7                                                         |       |           | 1/4      | LSI    |

|            |               |                                            | ideal input signals, reference to 12 Bit of sine period, f = 1 KHz |       |           |          |        |

| Noniu      | s Calculatio  | on                                         |                                                                    |       |           |          |        |

| 701        | Pnon          | Permissible Track deviation                | 16 periods, MPC = 0x4                                              |       |           | 10       | DE     |

|            |               | Master vs. Nonius                          | 32 periods, MPC = 0x5<br>64 periods, MPC = 0x6                     |       |           | 5<br>2.5 | DE     |

|            |               |                                            | referenced to 360° of Master sine period                           |       |           | 2.5      |        |

| Digita     | l Output Po   | rt PA13, MTC, SCL, SDA                     | · ·                                                                | Ш     | I         |          | 1      |

| 801        | Vs()hi        | Saturation Voltage hi Pins PA13            | ,Vs()hi = V(VPD) - V(), I() = -4 mA                                |       |           | 0.4      | V      |

| 802        | Vs()lo        | Saturation Voltage lo                      | I() = 4 mA versus VND                                              |       |           | 0.4      | V      |

| 803        | lsc()hi       | Short-Circuit Current hi Pins<br>PA13, MTC | V() = V(VND), 25 °C                                                | -90   | -50       |          | mA     |

| 804        | lsc()lo       | Short-Circuit Current lo                   | V() = V(VPD), 25 °C                                                | -     | 50        | 90       | mA     |

| 805        | tr()          | Rise Time                                  | CL = 50 pF                                                         |       |           | 60       | ns     |

| 806        | tf()          | Fall Time                                  | CL = 50 pF                                                         |       |           | 60       | ns     |

| 807        | llk(PA3)      | Leakage Current at PA3                     | MODEA=0, PA0 = hi                                                  | -5    |           | 5        | μA     |

| 808        | fclk(SCL)     | Frequency at SCL                           | normal mode                                                        |       | 80        |          | kHz    |

|            |               |                                            | during start-up                                                    |       | 70        |          | kHz    |

| Digita     |               | PA02, MTD, SCL, SDA                        |                                                                    |       |           |          |        |

| 901        | Vt()hi        | Threshold Voltage hi                       |                                                                    |       |           | 2        | V      |

| 902        | Vt()lo        | Threshold Voltage lo                       |                                                                    | 0.8   |           |          | V      |

| 903        | Vt()hys       | Hysteresis                                 | Vt()hys = Vt()hi - Vt()lo                                          | 150   |           |          | m∨     |

| 904        | lpu()         | Pull-Up Current Pins PA02,<br>MTD          | V() = 0 V V(VPD)-1 V                                               | -60   | -30       | -6       | μA     |

| 905        | lpu()         | Pull-Up Current Pins SCL, SDA              | V() = 0 V V(VPD)-1 V                                               | -800  | -300      | -80      | μA     |

| 906        | f()           | Permissible Input Frequency                |                                                                    |       |           | 10       | MH     |

| Analo      | g/Digital Ou  | itput Port PB02                            |                                                                    | ~     |           |          | •      |

| A01        | l()buf        | Analog Driver Current                      |                                                                    | -1    |           | 1        | mA     |

| A02        | fg()ana       | Analog Bandwidth                           |                                                                    |       | 100       |          | kH:    |

| A03        | lsc()hi,ana   | Analog Short-Circuit Current hi            | V() = V(VND)                                                       |       |           | -1.5     | mA     |

| A04        | lsc()lo,ana   | Analog Short-Circuit Current lo            | V() = V(VPD)                                                       | 1.5   |           |          | mA     |

| A05        | Rout(),ana    | Output Resistor, Analog Mode               | I() = 1 mA                                                         |       |           | 500      | Ω      |

Rev C1, Page 11/66

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VPD = VPA = 5 V  $\pm$ 10%, Tj = -40...125°C, IBP calibrated to 200  $\mu$ A, reference is VNA = VND, unless otherwise stated

| Item  | Symbol       | Parameter                       | Conditions                            |      |      |      | Unit |

|-------|--------------|---------------------------------|---------------------------------------|------|------|------|------|

| No.   |              |                                 |                                       | Min. | Тур. | Max. |      |

| A06   | Vs()hi,dig   | Digital Saturation Voltage hi   | Vs() = V(VPD) - V(), I() = -4 mA      |      |      | 0.5  | V    |

| A07   | Vs()lo,dig   | Digital Saturation Voltage lo   | I() = 4 mA                            |      |      | 0.5  | V    |

| A08   | lsc()hi,dig  | Short-Circuit Current hi        | V() = V(VPD)                          | -60  | -35  |      | mA   |

| A09   | lsc()lo,dig  | Short-Circuit Current lo        | V() = V(VND)                          |      | 45   | 70   | mA   |

| A10   | tr()         | Rise Time                       | CL = 50 pF                            |      |      | 50   | ns   |

| A11   | tf()         | Fall Time                       | CL = 50 pF                            |      |      | 50   | ns   |

| A12   | llk()        | Leakage Current                 | MODEB = 0x7                           | -5   |      | 5    | μA   |

| Analo | g/Digital Ou | tput Port PB3                   | ,                                     |      |      |      |      |

| B01   | l()buf       | Analog Driver Current           |                                       | -1   |      | 1    | mA   |

| B02   | fg()ana      | Analog Bandwidth                |                                       |      | 100  |      | kHz  |

| B03   | lsc()hi,ana  | Analog Short-Circuit Current hi | V() = V(VND)                          |      |      | -1.5 | mA   |

| B04   | lsc()lo,ana  | Analog Short-Circuit Current lo | V()=V(VPD)                            | 1.5  |      |      | mA   |

| B05   | Rout(),ana   | Output Resistor, Analog Mode    | I() = 1 mA                            |      |      | 500  | Ω    |

| B06   | Vs()lo,dig   | Digital Saturation Voltage lo   | I() = 4 mA                            |      |      | 0.5  | V    |

| B07   | lsc()lo,dig  | Short-Circuit Current lo        | V() = V(VND)                          |      | 45   | 70   | mA   |

| B08   | tr()         | Rise Time                       | CL = 50 pF                            |      |      | 50   | ns   |

| B09   | tf()         | Fall Time                       | CL = 50 pF                            |      |      | 50   | ns   |

| B10   | Ipu(PB3)     | Pull-Up Current                 | V() = 0 VV(VPD) - 1 V, MODEB = 0x00x3 | -60  | -30  | -6   | μA   |

| B11   | llk()        | Leakage Current                 | MODEB = 0x7                           | -5   |      | 5    | μA   |

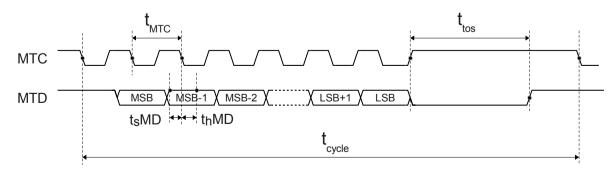

#### **OPERATING REQUIREMENTS: Multiturn Interface**

| ltem                           | Symbol Parameter Conditions |                                                      |          |   |      | Unit |    |

|--------------------------------|-----------------------------|------------------------------------------------------|----------|---|------|------|----|

| No.                            |                             |                                                      |          | м | lin. | Max. |    |

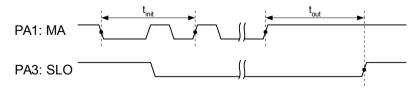

| Multiturn Interface (Figure 1) |                             |                                                      |          |   |      |      |    |

| 1001                           | t <sub>MTC</sub>            | Clock Period                                         |          |   | 6.4  |      | μs |

| 1002                           | t <sub>s</sub> MD           | Setup Time:<br>Data valid before MTC hi→lo           |          | 5 | 50   |      | ns |

| 1003                           | t <sub>h</sub> MD           | Hold Time: Data stable after MTC hi $\rightarrow$ lo |          | 5 | 50   |      | ns |

| 1004                           | t <sub>tos</sub>            | Timeout                                              |          |   | 2    | 0    | μs |

| 1005                           | t <sub>cycle</sub>          | Cycle Time                                           | CHK_MT=1 |   | 1    | 5    | ms |

Rev C1, Page 12/66

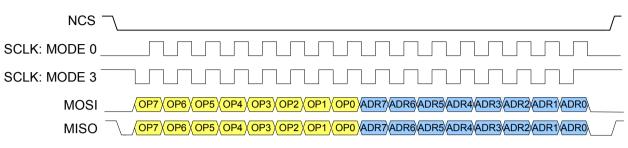

#### **OPERATING REQUIREMENTS: I/O Interface**

| ltem   | Symbol            | Parameter                                                              | Conditions                                                    |                               |                                                         | Unit     |

|--------|-------------------|------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------|---------------------------------------------------------|----------|

| No.    |                   |                                                                        |                                                               | Min.                          | Max.                                                    |          |

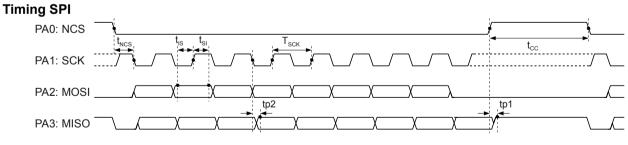

|        | terface (Fig      |                                                                        |                                                               |                               |                                                         |          |

| I101   | T <sub>SCK</sub>  | Permissible Clock Period                                               | see Elec. Char. No.: 906                                      | 1/                            | 'f()                                                    | ns       |

| 1102   | t <sub>NCS</sub>  | Setup Time: NCS lo before SCK hi $\rightarrow$ lo                      |                                                               | 50                            |                                                         | ns       |

| 1103   | tp1               | Propagation Delay: MISO hi after NCS lo $\rightarrow$ hi               |                                                               | 3                             | 0                                                       | ns       |

| I104   | t <sub>IS</sub>   | Setup Time:<br>MOSI stable before SCK lo $\rightarrow$ hi              |                                                               | 30                            |                                                         | ns       |

| 1105   | t <sub>SI</sub>   | Hold Time:<br>MOSI stable after SCK lo $\rightarrow$ hi                |                                                               | 30                            |                                                         | ns       |

| 1106   | tp2               | Propagation Delay: MISO stable after SCK hi $\rightarrow$ lo           |                                                               | 30                            |                                                         | ns       |

| 1107   | t <sub>cc</sub>   | Wait Time: between NCS lo $\rightarrow$ hi and NCS hi $\rightarrow$ lo |                                                               | 500                           |                                                         | ns       |

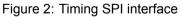

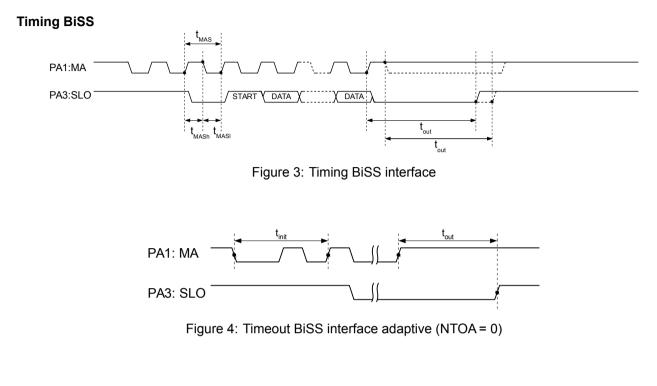

| BiSS-I | nterface (F       | igure 3, Figure 4)                                                     |                                                               |                               |                                                         |          |

| 1108   | t <sub>out</sub>  | Slave Timeout                                                          | NTOA = 0, adaptive, typ. t <sub>init</sub>                    | 1.5*t <sub>MAS</sub>          | 1.5*t <sub>MAS</sub> +<br>8/f <sub>osc</sub>            | ns       |

|        |                   |                                                                        | NTOA = 1, fixed                                               | 16000                         | 24000                                                   | ns       |

| 1109   | t <sub>MAS</sub>  | Permissible Clock Period                                               | NTOA = 0, adaptive, typ. t <sub>init</sub><br>NTOA = 1, fixed | 200<br>100                    |                                                         | ns<br>ns |

| 1110   | t <sub>MASh</sub> | Clock Signal Hi Level Duration                                         | NTOA = 0, adaptive, typ. t <sub>init</sub><br>NTOA = 1, fixed | 100<br>50                     | t <sub>out</sub><br>t <sub>out</sub>                    | ns<br>ns |

| 1111   | t <sub>MASI</sub> | Clock Signal Lo Level Duration                                         | NTOA = 0, adaptive, typ. t <sub>init</sub><br>NTOA = 1, fixed | 100<br>50                     |                                                         | ns<br>ns |

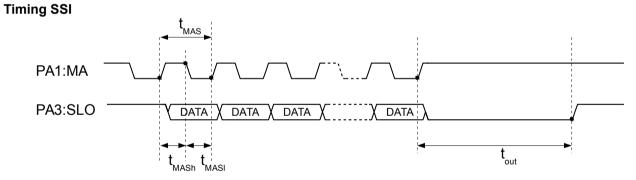

| SSI-In | terface (Fig      | gure 5), (Figure 6]                                                    |                                                               |                               |                                                         |          |

| 1112   | t <sub>out</sub>  | Timeout                                                                | NTOA = 1<br>NTOA = 0, adaptive, (not recommended)             | 16000<br>1.5*t <sub>MAS</sub> | 24000<br>1.5*t <sub>MAS</sub> +<br>8/f <sub>osc</sub> + | ns<br>ns |

| I113   | t <sub>MAS</sub>  | Permissible Clock Period                                               |                                                               | 250                           |                                                         | ns       |

| I114   | t <sub>MASh</sub> | Clock Signal Hi Level Duration                                         |                                                               | 125                           | t <sub>out</sub>                                        | ns       |

| I115   | t <sub>MASI</sub> | Clock Signal Lo Level Duration                                         |                                                               | 125                           |                                                         | ns       |

Rev C1, Page 13/66

Figure 5: Timing SSI interface (NTOA = 1)

Figure 6: Timeout SSI interface adaptive

Rev C1, Page 14/66

#### PRINCIPLE OF MEASUREMENT

An absolute position measuring system consists of a magnetized code carrier and an iC-MU150 which integrates Hall sensors for signal scanning, signal conditioning, and interpolation in one single device. iC-MU150 can be used in rotative and linear measurement systems.

Figure 7: Rotative position measurement system

Figure 8: Linear position measurement system

#### **Rotative measuring system**

The magnetic code carrier consists of two magnetic encoder tracks. The outer track comprises an even number of alternately magnetized poles and is used for high-precision position definition. This is thus called the master track. The second inside track has one pole pair less than the outer track and is thus referred to as the nonius track. This track is used to calculate an absolute position within one revolution of the pole disc. To this end, the difference in angle between the two tracks is calculated.

| Number of pole pairs       |      | 16    | 32    | 64    |

|----------------------------|------|-------|-------|-------|

| Master track diameter      | [mm] | 15.28 | 30.56 | 61.11 |

| Chip center to axis center | [mm] | 5.84  | 13.48 | 28.76 |

| Nonius track diameter      | [mm] | 8.08  | 23.36 | 53.92 |

| Master track pole width    | [mm] | 1.50  | 1.50  | 1.50  |

| Nonius track pole width    | [mm] | 0.85  | 1.18  | 1.34  |

Table 6: Pole disc dimensions in mm for rotative systems

Figure 9: Definition of system measurements

The Hall sensors of iC-MU150 span one pole pair of the code carrier. The pole width of the master track is defined by the distance of the Hall sensors and is 1.50 mm. The position of the sensors on the upper chip edge has been optimized for 32 pole pairs. Accordingly, the Hall sensors generate a periodic sine and cosine signal with a cycle length of 3.00 mm. The scan diameter can be computed from the number of pole pairs. The diameter of the pole disc although depends on other mechanical requirements and should be approx. 3 mm greater than the scan diameter. A specific diameter for the master and nonius tracks is derived depending on the number of configured pole pairs.

The distance between the hall sensors of the nonius track and the master track is stipulated as being 3.6 mm by the evaluation device. The scan diameters of the nonius track can be seen in Table 6.

#### Linear measuring system

With a linear nonius system the pole width of the master track is also 1.50 mm. The pole width of the nonius track is defined by the number of pole pairs with

$p_{nonius} = 1.50 \, mm * rac{number of poles_{master}}{number of poles_{nonius}}$

| Number of pole pairs         | 16    | 32    | 64    |

|------------------------------|-------|-------|-------|

| Master track pole width [mm] | 1.50  | 1.50  | 1.50  |

| Nonius track pole width [mm] | 1.600 | 1.548 | 1.524 |

Table 7: Linear scales, pole widths in mm

#### **CONFIGURATION PARAMETERS**

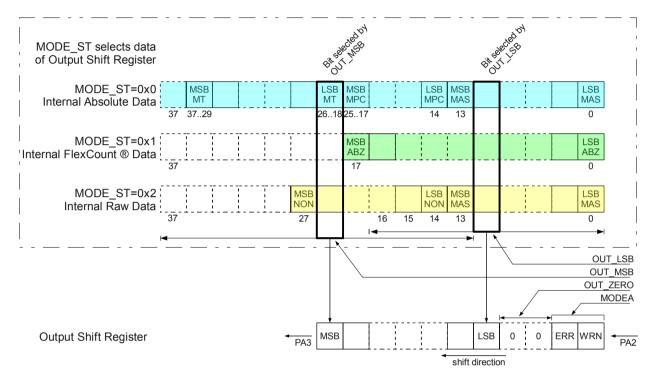

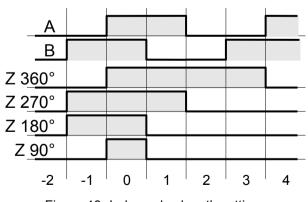

#### Analog parameters (valid for all channels) Bias current settings (p. 20) CIBM: ENAC: Amplitude control unit activation (p. 21) Signal conditioning GC M: Master gain range selection (p. 20) GF M: Master gain (p. 20) GX\_M: Master cosine signal gain adjustment (p. 20) VOSS M: Master sine offset adjustment (p. 21) VOSC M: Master cosine offset adjustment (p. 21) PH\_M: Master phase adjustment (p. 21) Master phase adjustment range (p. 21) PHR\_M: GC\_N: Nonius gain range selection (p. 20) GF N: Nonius gain (p. 20) GX\_N: Nonius cosine signal gain adjustment (p. 20) VOSS N: Nonius sine offset adjustment (p. 21) VOSC N: Nonius cosine offset adjustment (p. 21) PH N: Nonius phase adjustment (p. 21) PHR N: Nonius phase adjustment range (p. 21) **Digital parameters** TEST: Adjustment modes/iC-Haus test modes (p. 22) CRC16: EEPROM configuration data checksum (p. 24) EEPROM offset and preset data CRC8: checksum (p. 25) NCHK\_CRC: Cyclic check of CRC16 and CRC8 (p. 25) BANKSEL: Serial Access: Bank register (p. 50) RPL: Register Access Control (p. 54) RPL RESET: Serial Access: Register for reset register access restriction (p. 54) EVENT\_COUNT: Serial Access: Event counter (p. 59) HARD REV: serial address: revision code (p. 53) Configurable I/O interface MODEA: I/O port A configuration (p. 28) MODEB: I/O port B configuration (p. 28) NTOA: Adaptive Timeout (p.31) Configurable commands to pin PA0 A PA0 CONF: (p. 61) ROT ALL: Code direction (p. 30) OUT\_MSB: Output shift register configuration: MSB used bits (p. 30) Output shift register configuration: LSB OUT\_LSB: used bits (p. 30) OUT\_ZERO: Output shift register configuration: number of zeros inserted after the used bits and before an error/warning (p. 30) MODE ST: Data output (p. 29) GSSI: Gray/binary data format (p. 33) RSSI: Ring operation (p. 33)

#### . . .

| Multiturn in | terface                                                  |

|--------------|----------------------------------------------------------|

| MODE_MT:     | Multiturn mode (p. 42)                                   |

| SBL_MT:      | Multiturn synchronization bit length (p. 42)             |

| CHK_MT:      | Cyclic check of the multiturn value (p. 43)              |

| GET MT:      | MT interface daisy chain (S. 45)                         |

| ROT_MT:      | Code direction external multiturn (p. 43)                |

| ESSI_MT:     | Error Bit external multiturn (p. 43)                     |

| SPO_MT:      | Offset external multiturn (p. 43)                        |

| Converter a  | nd nonius calculation                                    |

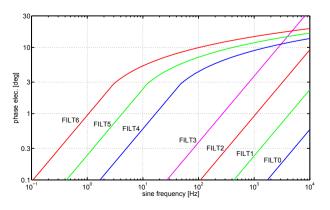

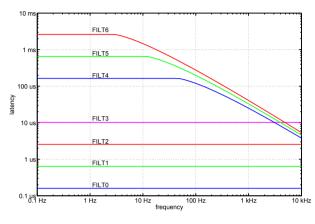

| FILT:        | Digital filter settings (p. 39)                          |

| MPC:         | Master period count (p. 39)                              |

| LIN:         | Linear scanning (p. 40)                                  |

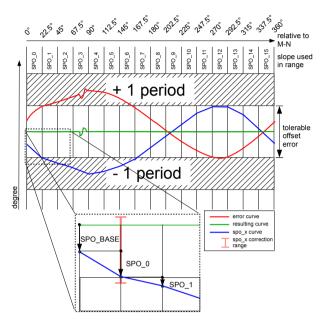

| SPO_x:       | Offset of nonius to master                               |

| -            | (x=BASE,0-14) (p. 40)                                    |

| NCHK_NON:    | Cyclic check of the nonius value (low                    |

|              | active) (p. 41)                                          |

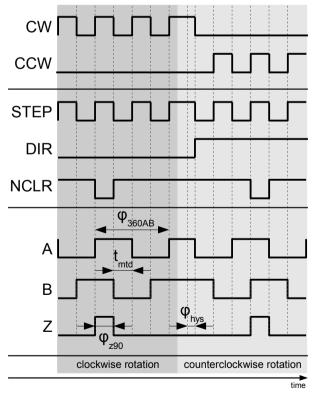

| Incremental  | output ABZ, STEP/DIR and CW/CCW                          |

| RESABZ:      | Incremental interface resolution                         |

|              | ABZ,STEP-DIR,CW/CCW (p. 46)                              |

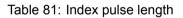

| LENZ:        | Index pulse length (p. 47)                               |

| INV_A:       | A/STEP/CW signal inversion (p. 47)                       |

| INV_B:       | B/DIR/CCW signal inversion (p. 47)                       |

| INV_Z:       | Z/NCLR signal inversion (p. 47)                          |

| SS_AB:       | System AB step size (p. 48)                              |

| FRQAB:       | AB output frequency (p. 48)                              |

| CHYS_AB:     | Converter hysteresis (p. 48)                             |

| ENIF_AUTO:   | Incremental interface enable (p. 48)                     |

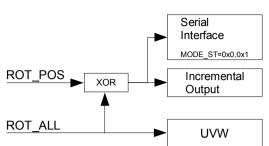

| UVW comm     | utation signals                                          |

| PPUVW:       | Number of commutation signal pole                        |

|              | pairs (p. 49)                                            |

| PP60UVW:     | Commutation signal phase position                        |

|              | (p. 49)                                                  |

| OFF_UVW:     | Commutation signal start angle (p. 49)                   |

| OFF_COM:     | serial address: absolute position offset                 |

|              | for UVW calculation engine changed by $ranging (S = 40)$ |

|              | nonius (S. 49)                                           |

|              | mand registers and error monitoring                      |

| CMD_MU:      | serial address: command register (p. 58)                 |

| STATUS0:     | serial address: status register 0 (p. 56)                |

| STATUS1:     | serial address: status register 1 (p. 56)                |

| CFGEW:       | Error and warning bit configuration                      |

|              | (p. 57)                                                  |

| EMTD:        | Minimum error message duration (p. 57)                   |

| ACC_STAT:    | Output configuration status register (S. 56)             |

| ACRM RES:    |                                                          |

| AURIVI_RES   | amplitude errors (p. 41)                                 |

|              |                                                          |

Rev C1, Page 16/66

#### **BiSS-ID/Profile-ID**

| <b>BiSS-ID/Prot</b> | file-ID                 | ROT_POS: | Code direction for ABZ calculation                             |

|---------------------|-------------------------|----------|----------------------------------------------------------------|

| DEV_ID:             | Device ID (p. 19)       |          | engine and serial absolute                                     |

| MFG_ID:             | Manufacturer ID (p. 19) | OFE AB7. | interface(p. 30)<br>Offset Absolute position offset for ABZ    |

| EDSBANK:            | EDSBANK (p. 19)         |          | calculation engine (p. 62)                                     |

| PROFILE_ID:         | Profile ID (p. 19)      | OFF_POS: | serial address: absolute position offset                       |

| SERIAL:             | Serial number (p. 19)   |          | for ABZ calculation engine changed by nonius/multiturn (p. 62) |

| D                   | •                       |          |                                                                |

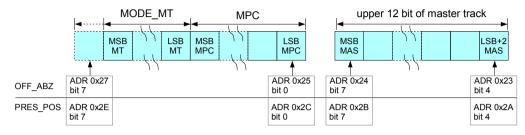

#### **Preset function**

PRES\_POS: Preset position for ABZ section (p. 62)

#### Rev C1, Page 17/66

#### **REGISTER ASSIGNMENTS (EEPROM)**

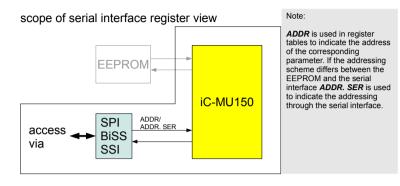

Figure 10: Scope of register mapping EEPROM

#### **Register assignment (EEPROM)**

| OVERV     | RVIEW       |             |             |          |               |           |            |       |

|-----------|-------------|-------------|-------------|----------|---------------|-----------|------------|-------|

| Addr      | Bit 7       | Bit 6       | Bit 5       | Bit 4    | Bit 3         | Bit 2     | Bit 1      | Bit 0 |

| Signal C  | onditioning |             |             |          |               |           |            |       |

| 0x00      | GC_I        | M(1:0)      |             |          | GF_N          | 1(5:0)    |            |       |

| 0x01      |             |             |             |          | GX_M(6:0)     |           |            |       |

| 0x02      |             |             | VOSS_M(6:0) |          |               |           |            |       |

| 0x03      |             |             | VOSC_M(6:0) |          |               |           |            |       |

| 0x04      | PHR_M       |             | PH_M(6:0)   |          |               |           |            |       |

| 0x05      | ENAC        |             |             |          |               |           | A(3:0)     |       |

| 0x06      | GC_I        | N(1:0)      |             |          | GF_N          | l(5:0)    |            |       |

| 0x07      |             | GX_N(6:0)   |             |          |               |           |            |       |

| 0x08      |             |             | VOSS_N(6:0) |          |               |           |            |       |

| 0x09      |             | VOSC_N(6:0) |             |          |               |           |            |       |

| 0x0A      | PHR_N       |             |             |          | PH_N(6:0)     |           |            |       |

| Digital F | Parameters  |             |             |          |               |           |            |       |

| 0x0B      |             |             | MODEB(2:0)  |          | NTOA          |           | MODEA(2:0) |       |

| 0x0C      |             |             |             | CFGE     | W(7:0)        |           |            |       |

| 0x0D      | ACC_STAT    | NCHK_CRC    | NCHK_NON    | ACRM_RES |               |           | EMTD(2:0)  |       |

| 0x0E      | ESSI_I      | MT(1:0)     | ROT_MT      | LIN      |               |           | FILT(2:0)  |       |

| 0x0F      |             | SPO_N       | . ,         |          |               |           | C(3:0)     |       |

| 0x10      | GET_MT      | CHK_MT      |             | ИТ(1:0)  |               |           | _MT(3:0)   |       |

| 0x11      | 0           | UT_ZERO(2   | ,           |          | 0             | UT_MSB(4: | ,          |       |

| 0x12      | GSSI        | RSSI        | MODE_       | _ST(1:0) | OUT_LSB(3:0)  |           |            |       |

| 0x13      |             |             |             |          | BZ(7:0)       |           |            |       |

| 0x14      |             | 1           | 1           |          | BZ(15:8)      |           |            |       |

| 0x15      | ROT_ALL     |             |             | .B(1:0)  | ENIF_AUTO     |           | FRQAB(2:0) |       |

| 0x16      |             | Z(1:0)      | CHYS_       | AB(1:0)  | PP60UVW       | INV_A     | INV_B      | INV_Z |

| 0x17      | RPL         | .(1:0)      |             |          | PPUV          | W(5:0)    |            |       |

| TEST      | 1           |             |             |          |               |           |            |       |

| 0x18      |             |             |             | TES      | Г(7:0)        |           |            |       |

| TRACK-    | OFFSET      |             |             |          |               |           |            |       |

| 0x19      |             |             | 0(3:0)      |          | SPO_BASE(3:0) |           |            |       |

| 0x1A      |             | SPO_        | 2(3:0)      |          |               | SPO_      | _1(3:0)    |       |

Rev C1, Page 18/66

| OVERV    | EW                             |                                                              |               |                  |                      |       |         |         |

|----------|--------------------------------|--------------------------------------------------------------|---------------|------------------|----------------------|-------|---------|---------|

| Addr     | Bit 7                          | Bit 6                                                        | Bit 5         | Bit 4            | Bit 3                | Bit 2 | Bit 1   | Bit 0   |

| 0x1B     |                                | SPO_                                                         | 4(3:0)        | I.               | SPO_3(3:0)           |       |         |         |

| 0x1C     |                                | SPO_                                                         | 6(3:0)        |                  | SPO_5(3:0)           |       |         |         |

| 0x1D     |                                | SPO_                                                         |               |                  |                      |       | _7(3:0) |         |

| 0x1E     |                                | SPO_                                                         |               |                  |                      |       | _9(3:0) |         |

| 0x1F     |                                | SPO_                                                         |               |                  |                      |       | 11(3:0) |         |

| 0x20     |                                | SPO_                                                         | 4(3:0)        |                  |                      | SPO_  | 13(3:0) |         |

| CRC16    |                                |                                                              |               |                  |                      |       |         |         |

| 0x21     |                                | CRC16(15:8)                                                  |               |                  |                      |       |         |         |

| 0x22     |                                |                                                              |               | CRC <sup>2</sup> | 16(7:0)              |       |         |         |

| OFFSET   | PRESET                         |                                                              |               |                  |                      |       |         |         |

| 0x23     |                                | OFF_A                                                        | BZ(3:0)       |                  |                      |       |         | ROT_POS |

| 0x24     |                                |                                                              |               |                  | BZ(11:4)             |       | -       |         |

| 0x25     |                                |                                                              |               |                  | 3Z(19:12)            |       |         |         |

| 0x26     |                                |                                                              |               |                  | 3Z(27:20)            |       |         |         |

| 0x27     | —                              |                                                              |               | 3Z(35:28)        |                      |       |         |         |

| 0x28     | OFF_UVW(3:0)                   |                                                              |               |                  |                      |       |         |         |

| 0x29     |                                |                                                              |               | OFF_U            | √W(11:4)             | 1     | 1       |         |

| 0x2A     |                                | PRES_POS(3:0)                                                |               |                  |                      |       |         |         |

| 0x2B     |                                | PRES_POS(11:4)                                               |               |                  |                      |       |         |         |

| 0x2C     |                                |                                                              |               |                  | OS(19:12)            |       |         |         |

| 0x2D     |                                |                                                              |               | _                | OS(27:20)            |       |         |         |

| 0x2E     |                                |                                                              |               | PRES_P           | OS(35:28)            |       |         |         |

| CRC8     |                                |                                                              |               |                  |                      |       |         |         |

| 0x2F     |                                |                                                              |               | CRC              | 8(7:0)               |       |         |         |

| PA0_CO   | NF                             |                                                              |               |                  |                      |       |         |         |

| 0x30     |                                |                                                              |               | PA0_C0           | ONF(7:0)             |       |         |         |

| BiSS Pro | ofile and Seri                 | al number                                                    |               |                  |                      |       |         |         |

| 0x31     |                                |                                                              |               |                  | (7:0) = 0x01         |       |         |         |

| 0x32     | PROFILE_ID(7:0)                |                                                              |               |                  |                      |       |         |         |

| 0x33     |                                |                                                              |               |                  | E_ID(15:8)           |       |         |         |

| 0x34     |                                |                                                              |               |                  | AL(7:0)              |       |         |         |

| 0x35     |                                | SERIAL(15:8)                                                 |               |                  |                      |       |         |         |

| 0x36     | SERIAL(23:16)                  |                                                              |               |                  |                      |       |         |         |

| 0x37     |                                |                                                              |               | SERIA            | L(31:24)             |       |         |         |

|          | dentification                  |                                                              |               |                  |                      |       |         |         |

| 0x38     | DEV_ID(7:0)                    |                                                              |               |                  |                      |       |         |         |

| 0x39     | DEV_ID(15:8)                   |                                                              |               |                  |                      |       |         |         |

| 0x3A     | DEV_ID(23:16)<br>DEV_ID(31:24) |                                                              |               |                  |                      |       |         |         |

| 0x3B     |                                |                                                              |               |                  | · /                  |       |         |         |

| 0x3C     |                                |                                                              |               |                  | D(39:32)<br>D(47:40) |       |         |         |

| 0x3D     |                                |                                                              |               |                  | . ,                  |       |         |         |

| 0x3E     |                                |                                                              |               |                  | ID(7:0)<br>D(15:8)   |       |         |         |

| 0x3F     | Pegister as                    | signment for                                                 | ential access |                  |                      | )     |         |         |

| Notes:   | ivegister as                   | gister assignment for serial access through SPI/BiSS s.p. 50 |               |                  |                      |       |         |         |

#### Rev C1, Page 19/66

#### Special BiSS registers

For further information on parameters, see BiSS Interface Protocol Description (C Mode) www.ichaus.de/product/iC-MU150.

| DEV_ID(7:0)    | Addr. 0x38; bit 7:0     |

|----------------|-------------------------|

|                | Addr. SER:0x78; bit 7:0 |

| DEV_ID(15:8)   | Addr. 0x39; bit 7:0     |

|                | Addr. SER:0x79; bit 7:0 |

| DEV_ID(23:16   | 6) Addr. 0x3A; bit 7:0  |

|                | Addr. SER:0x7A; bit 7:0 |

| DEV_ID(31:24   | 4) Addr. 0x3B; bit 7:0  |

|                | Addr. SER:0x7B; bit 7:0 |

| DEV_ID(39:32   | 2) Addr. 0x3C; bit 7:0  |

|                | Addr. SER:0x7C; bit 7:0 |

| DEV_ID(47:40   | 0) Addr. 0x3D; bit 7:0  |

|                | Addr. SER:0x7D; bit 7:0 |

| Code           | Description             |

| 0x000000000000 |                         |

|                | DEV_ID                  |

| 0xFFFFFFFFFFFF |                         |

|                |                         |

Table 9: Device ID

| MFG_ID(7:0) | Addr. 0x3E; bit 7:0     |  |

|-------------|-------------------------|--|

|             | Addr. SER:0x7E; bit 7:0 |  |

| MFG_ID(15:8 | ) Addr. 0x3F; bit 7:0   |  |

|             | Addr. SER:0x7F; bit 7:0 |  |

| Code        | Description             |  |

| 0x0000      |                         |  |

|             | MFG_ID                  |  |

| 0xFFFF      |                         |  |

Table 10: BiSS Manufacturer ID

| EDSBANK(7: | o) Addr. 0x31; bit 7:0                                                                                 |  |

|------------|--------------------------------------------------------------------------------------------------------|--|

| EDSBANK(7: | 0) Addr. SER:0x41; bit 7:0                                                                             |  |

| Code       | Description                                                                                            |  |

| 0x00       | no EDS                                                                                                 |  |

| 0x01       |                                                                                                        |  |

|            | EDSBANK pointer to first EDS bank                                                                      |  |

| 0xFE       |                                                                                                        |  |

| 0xFF       | no EDS                                                                                                 |  |

| Note:      | recommended value 0x02, in this case an additional sensor like iC-PVL can use BANK 1 for configuration |  |

Table 11: EDSBANK: Start of EDS-part

| PROFILE_ID(7:0)  |       | Addr. 0x32; bit 7:0     |  |

|------------------|-------|-------------------------|--|

|                  |       | Addr. SER:0x42; bit 7:0 |  |

| PROFILE_ID(15:8) |       | Addr. 0x33; bit 7:0     |  |

|                  |       | Addr. SER:0x43; bit 7:0 |  |

| Code             | Desci | Description             |  |

| 0x0000           |       |                         |  |

| PROFIL           |       | FILE_ID                 |  |

| 0xFFFF           |       |                         |  |

Table 12: Profile ID

| SERIAL(7:0)       Addr. 0x34; bit 7:0         Addr. SER:0x44; bit 7:0         SERIAL(15:8)       Addr. 0x35; bit 7:0         Addr. SER:0x45; bit 7:0         Addr. SER:0x46; bit 7:0         SERIAL(23:16)       Addr. 0x36; bit 7:0         SERIAL(31:24)       Addr. 0x37; bit 7:0         Code       Description         0x00000000       Extended |              |                         |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------|--|

| SERIAL(15:8)       Addr. 0x35; bit 7:0         Addr. SER:0x45; bit 7:0         SERIAL(23:16)       Addr. 0x36; bit 7:0         Addr. SER:0x46; bit 7:0         Addr. SER:0x46; bit 7:0         Addr. 0x37; bit 7:0         Addr. SER:0x47; bit 7:0         Code       Description                                                                     | SERIAL(7:0)  | Addr. 0x34; bit 7:0     |  |

| Addr. SER:0x45; bit 7:0         SERIAL(23:16)       Addr. 0x36; bit 7:0         Addr. SER:0x46; bit 7:0         Addr. 0x37; bit 7:0         Addr. SER:0x47; bit 7:0         Code       Description                                                                                                                                                    |              | Addr. SER:0x44; bit 7:0 |  |

| SERIAL(23:16)         Addr. 0x36; bit 7:0           Addr. SER:0x46; bit 7:0           SERIAL(31:24)         Addr. 0x37; bit 7:0           Addr. SER:0x47; bit 7:0           Code         Description                                                                                                                                                  | SERIAL(15:8) | Addr. 0x35; bit 7:0     |  |

| Addr. SER:0x46; bit 7:0       SERIAL(31:24)     Addr. 0x37; bit 7:0       Addr. SER:0x47; bit 7:0       Code     Description                                                                                                                                                                                                                          |              | Addr. SER:0x45; bit 7:0 |  |

| SERIAL(31:24)         Addr. 0x37; bit 7:0           Addr. SER:0x47; bit 7:0           Code           Description                                                                                                                                                                                                                                      | SERIAL(23:16 | 6) Addr. 0x36; bit 7:0  |  |

| Addr. SER:0x47; bit 7:0 Code Description                                                                                                                                                                                                                                                                                                              |              | Addr. SER:0x46; bit 7:0 |  |

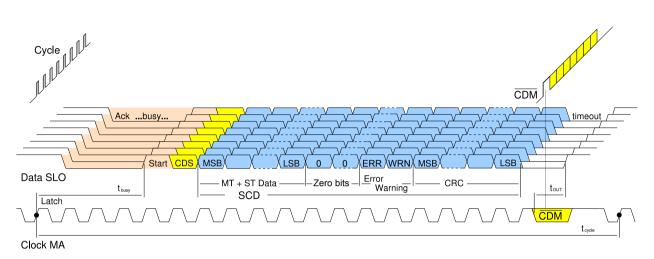

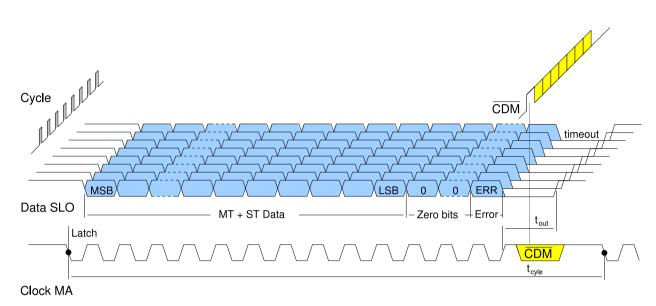

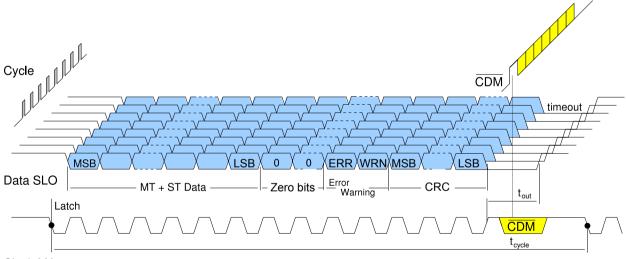

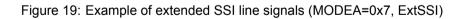

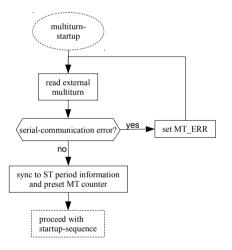

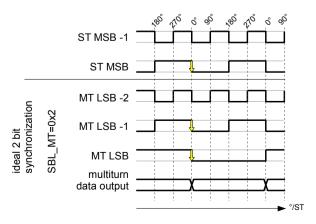

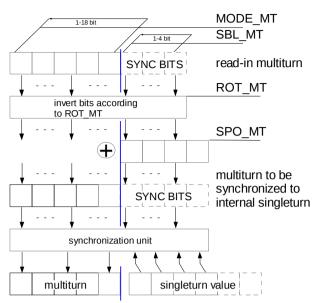

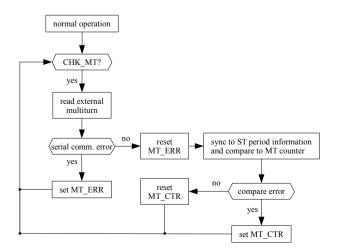

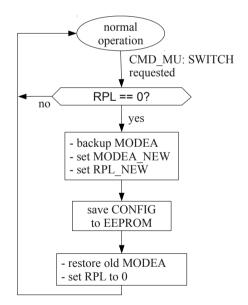

| Code Description                                                                                                                                                                                                                                                                                                                                      | SERIAL(31:24 | 4) Addr. 0x37; bit 7:0  |  |